# *NAMIBIA UNIVERSITY*

OF SCIENCE AND TECHNOLOGY

## **FACULTY OF COMPUTING AND INFORMATICS**

DEPARTMENT OF COMPUTER SCIENCE

| QUALIFICATION: BACHELOR OF COMPUTER SCIENCE, BACHELOR OF COMPUTER IN CYBER |                      |  |

|----------------------------------------------------------------------------|----------------------|--|

| SECURITY & BACHELOR OF INFORMATICS                                         |                      |  |

| QUALIFICATION CODE: 07BACS, 07BCCS &                                       | LEVEL: 5             |  |

| 07BAIF                                                                     | LEVEL: 3             |  |

| COURSE: COMPUTER ORGANISATION                                              | COURSE CODE: COA511S |  |

| AND ARCHITECTURE                                                           |                      |  |

| DATE: JUNE 2019                                                            | PAPER: THEORY        |  |

|                                                                            |                      |  |

| DURATION: 2H                                                               | MARKS: 100           |  |

|                                                                            |                      |  |

| FIRST OPPORTUNITY EXAMINATION QUESTION PAPER |                        |  |

|----------------------------------------------|------------------------|--|

| EXAMINER(S)                                  | MR. JULIUS SILAA       |  |

|                                              | MS. ALBERTINA SHILONGO |  |

|                                              | MS. JOVITA MATEUS      |  |

|                                              | MR. ELIEZER MBAEVA     |  |

|                                              | MS. EUNICE MBASUVA     |  |

|                                              | MR. VEERAB PADURI      |  |

|                                              | MR. JEREMIAH LUMBASI   |  |

|                                              | MR. GABRIEL NHINDA     |  |

|                                              | MS. RUUSA IIPINGE      |  |

| MODERATOR:                                   | MR. SIMON MUCHINENYIKA |  |

### THIS QUESTION PAPER CONSISTS OF 5 PAGES

(Excluding this front page)

#### **INSTRUCTIONS**

- 1. Answer ALL the questions on the answer scripts.

- 2. Write clearly and neatly.

- 3. Number the answers clearly.

### **PERMISSIBLE MATERIALS**

1. Calculator.

#### SECTION A [15 MARKS]: Each Question Weighs 1 Mark.

- 1. The AGP expansion cards found on the on the motherboard are superior to PCI Express (PCIe). [True/False]

- 2. The SRAM is the building block for level 1 Cache memory [True/False]

- 3. The first major change in the electronic computer came with the replacement of vacuum tube with the transistor. [True/False]

- 4. Architectural attributes include hardware details transparent to the programmer. [True/False]

- 5. The speed of a processor is dictated by the pulse frequency produced by the clock, measured in cycles per second, or Hertz (Hz). [True/False]

- 6. The I/O function includes a control and timing requirement, to coordinate the flow of traffic between internal resources and external devices. [True/False]

- 7. Pipelining is a means of introducing parallelism into the essential sequential nature of a machine-instruction program. [True/False]

- 8. Addition and subtraction can be performed on numbers in two complement notation by treating them as unsigned integers. [True/False]

- Although convenient for computers, the binary system is exceedingly cumbersome for human beings. [True/False]

- 10. In the Direct Memory Access (DMA) mode, the I/O module and main memory exchange data directly, without processor involvement. [True/False]

- 11. Hexadecimal notation is more compact than binary notation. [True/False]

- 12. In a system without virtual memory, the effective address is a virtual address or a register. [True/False]

- 13. Segmentation is usually visible to the programmer and is provided as a convenience for organizing programs and data and as a means for associating privilege and protection attributes with instructions and data. [True/False]

- 14.Instruction pipelining is a powerful technique for enhancing performance but requires careful design to achieve optimum results with reasonable complexity. [True/False]

- 15. The XOR operator yields false if both its operands are False. [True/False]

| 9.The                | specifies the operation to be pe                                      | errormea.                                                          |  |

|----------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|--|

|                      | A. source operand reference                                           | B. opcode                                                          |  |

|                      | C. next instruction reference                                         | D. processor register                                              |  |

| 10. All instruct     | tions in the ARM architecture are                                     | bits long and follow a regula                                      |  |

| Torritae.            | A. 8                                                                  | B. 16                                                              |  |

|                      | C. 32                                                                 | D. 64                                                              |  |

| 11.The<br>processor. |                                                                       | controls the movement of data and instructions into and out of the |  |

|                      | A. control unit                                                       | B. ALU                                                             |  |

|                      | C. shifter                                                            | D. branch                                                          |  |

| 12.The               | contains the address of an in                                         | struction to be fetched.                                           |  |

|                      | A. instruction register                                               | B. memory address register                                         |  |

|                      | C. memory buffer register                                             | D. program counter                                                 |  |

|                      | registers may be used only to hold of an operand address.             | data and cannot be employed in the                                 |  |

|                      | A. General purpose                                                    | B. Data                                                            |  |

|                      | C. Address                                                            | D. Condition code                                                  |  |

|                      | _ is a dispatch able unit of work w context and its own data area for |                                                                    |  |

|                      | A. Process                                                            | B. Process switch                                                  |  |

|                      | C. Thread                                                             | D. Thread switch                                                   |  |

| 15. A                |                                                                       | s use of more, and more fine-grained                               |  |

| p.peiiile 3          |                                                                       |                                                                    |  |

|                      | A. parallel                                                           | B. superpipe lined                                                 |  |

|                      | C. superscalar                                                        | D. hybrid                                                          |  |

#### Question 4

- a) Give any two examples of each of the following types of Digital circuits (4 Marks)

- i) Combinational

- ii) Sequential

- b) Explain one major difference between Combinational and Sequential circuits.

(4 Marks)

- c) Why does the program execution speed generally increase as the number of general purpose registers increase? (4 Marks)

#### Question 5

Soccer fans around the world are debating that Messi will score more international goals than Neymar in upcoming tournaments. Messi's fans think he will lead by 13 goals. If Messi happen to scores 44 goals, then apply 2's complement method to compute the number of Neymar's goals. Show your calculation step by step.

(8 Marks)

#### Question 6

a) List any 4 types of basic logical gates

- (2 Marks)

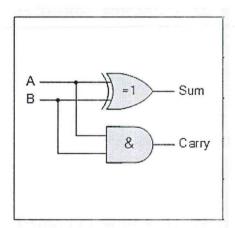

- b) Identify(name) the following combinational circuit found in the ALU.

- (2 Marks)

c) Draw a truth table depicting the circuit above. As shown in the diagram above your truth table should include two inputs and two outputs. Remember the output depend on the types of gate shown in the circuit. (8 Marks)

\*\*\*\*\*END OF PAPER\*\*\*\*